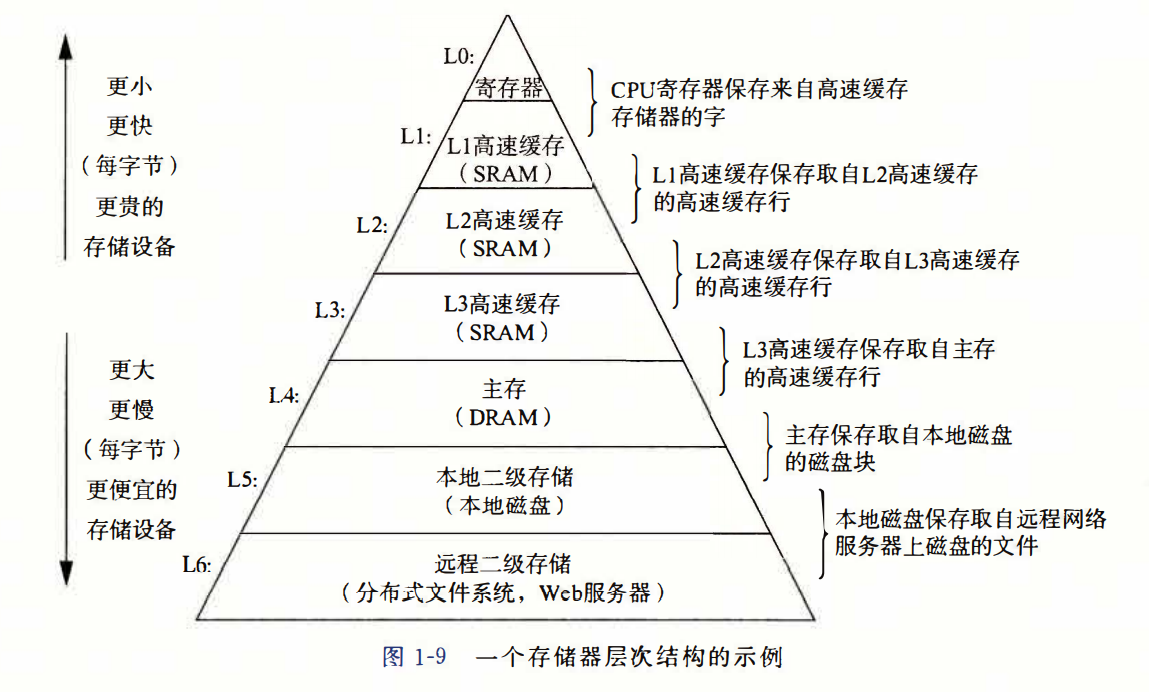

CSAPP-06存储器层次结构

存储技术:

- SRAM

- DRAM

- ROM

- 旋转的/固态的硬盘

重点:

- 高速缓存存储器:对应用程序的性能影响最大。

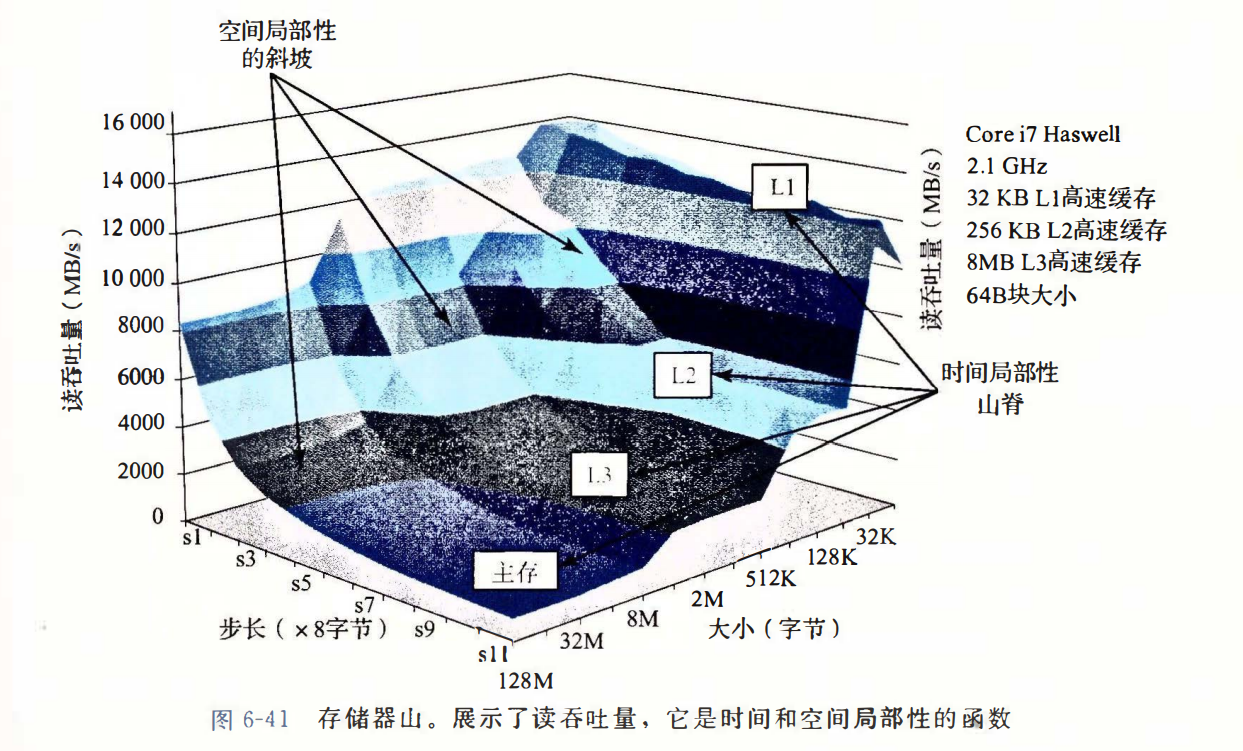

- 局部性

- 存储器山

存储技术

随机访问存储器

随机访问存储器(Random-Access Memory,RAM):

- 静态RAM(SRAM):快、贵,作为高速缓存存储器,既可以在CPU芯片上,也可以在片下。一般不会超过几兆字节。

- 动态RAM(DRAM):慢、便宜,作为主存以及图形系统的帧缓冲区。几百或几千兆字节。

静态RAM

SRAM将每个位存储在一个双稳态的(bistable)存储器单元里。每个单元是用一个六晶体管电路来实现的。这个电路有这样一个属性,它可以无限期地保持在两个不同的电压配置或状态之一。其他任何状态都是不稳定的——从不稳定状态开始,电路会迅速地转移到两个稳定状态中的一个。

由于SRAM存储器单元的双稳态特性,只要有电,它就会永远地保持它的值。即使有干扰(例如电子噪音)来扰乱电压,当干扰消除时,电路就会恢复到稳定值。

动态RAM

DRAM将每个位存储为对一个电容的充电。这个电容非常小。

DRAM存储器单元对干扰非常敏感,当电容的电压被扰乱之后,它就永远不会恢复了。暴露在光线下会导致电容电压改变。实际上,数码照相机和摄像机中的传感器本质上就是DRAM单元的阵列。

内存模块

DRAM芯片封装在内存模块中,它插到主板的扩展槽上。Core i7系统使用的240个引脚的双列直插内存块,它以64位为块传送数据到内存控制器和从内存控制器传出数据。

非易失性存储器

- 可檫写编程ROM(Erasable Programmable ROM,EPROM);

- 闪存(flash memory),基于EEPROM

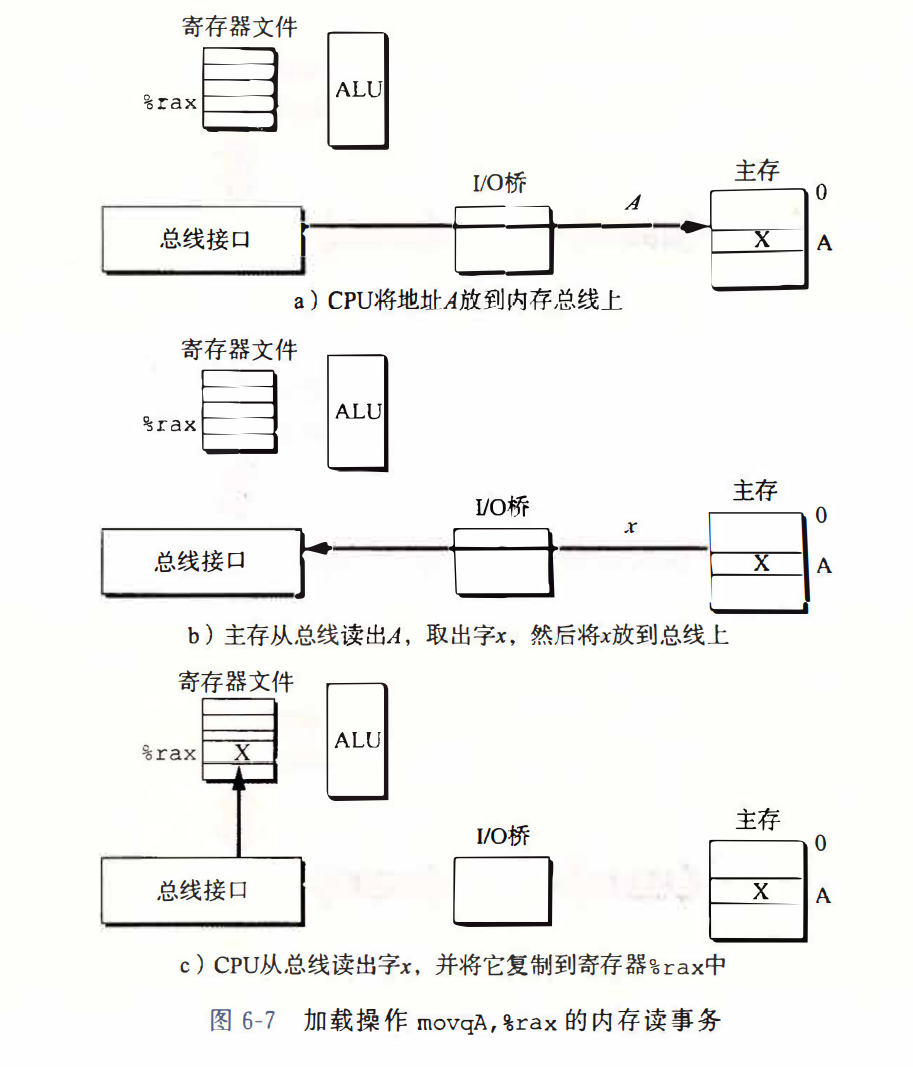

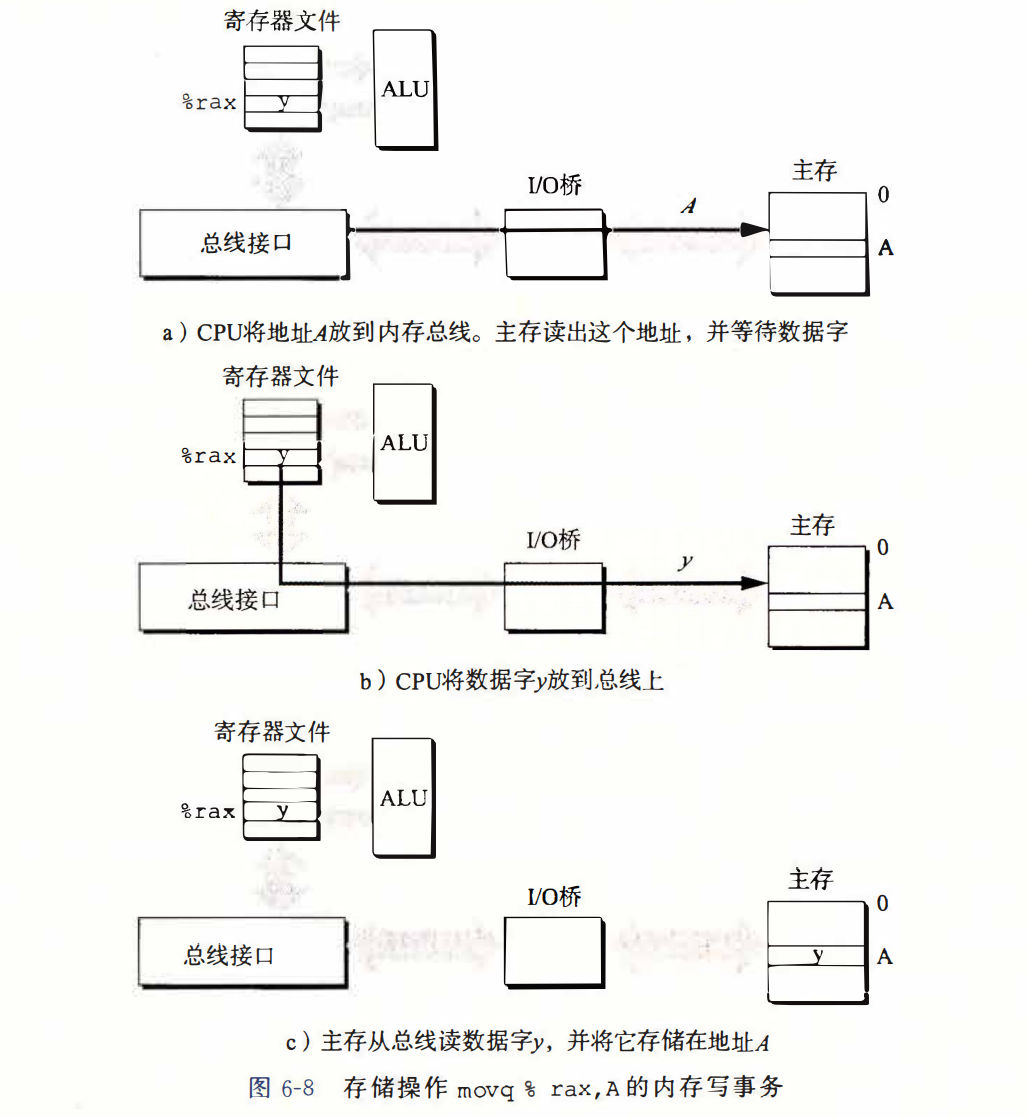

访问主存

数据流通过称为总线(bus)的共享电子电路在处理器和DRAM主存之间来来回回。

- 总线事务(bus transaction)

- 读事务

- 写事务

磁盘存储

连接IO设备

- 通用串行总线(Universal Serial Bus,USB)

- 图像卡(或适配器)

- 主机总线适配器

访问磁盘

- 内存映射I/O(memory-mapped I/O)。

- 直接内存访问(Direct Memory Access,DMA)。

固态硬盘

固态硬盘(Solid State Disk,SSD)是一种基于闪存的存储技术。

局部性

一个编写良好的计算机程序常常具有良好的局部性。也就是,它们倾向于引用邻近于其他最近引用过的数据项的数据项,或者最近引用过的数据项本身。

- 时间局部性

- 空间局部性

对程序数据引用的局部性

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

#define M 3

#define N 2

// 具有良好局部性的程序

// 地址: 0 4 8 12 16 20

// 内容: a00 a01 a02 a10 a11 a12

// 访问顺序:1 2 3 4 5 6

int sum_array_rows(int a[M][N])

{

int i, j, sum = 0;

for (i = 0; i < M; i++)

{

for (j = 0; j < N; j++)

{

sum += a[i][j];

}

}

return sum;

}

// 空间局部性很差

// 地址: 0 4 8 12 16 20

// 内容: a00 a01 a02 a10 a11 a12

// 访问顺序:1 3 5 2 4 6

int sum_array_cols(int a[M][N])

{

int i, j, sum = 0;

for (j = 0; j < N; j++)

for (i = 0; i < M; i++)

{

{

sum += a[i][j];

}

}

return sum;

}

取指令的局部性

因为程序指令是存放在内存中的,CPU必须取出(读出)这些指令。

上面for循环体里的指令是按照连续的内存顺序执行的,因此循环有良好的空间局部性。因为循环体会被执行多次,所以它也有很好的时间局部性。

代码区区别于程序数据的一个重要属性是在运行时它时不能被修改的。当程序正在执行时,CPU只从内存中读出它的指令,CPU很少会重写或修改这些指令。

存储器层次结构

高速缓存存储器

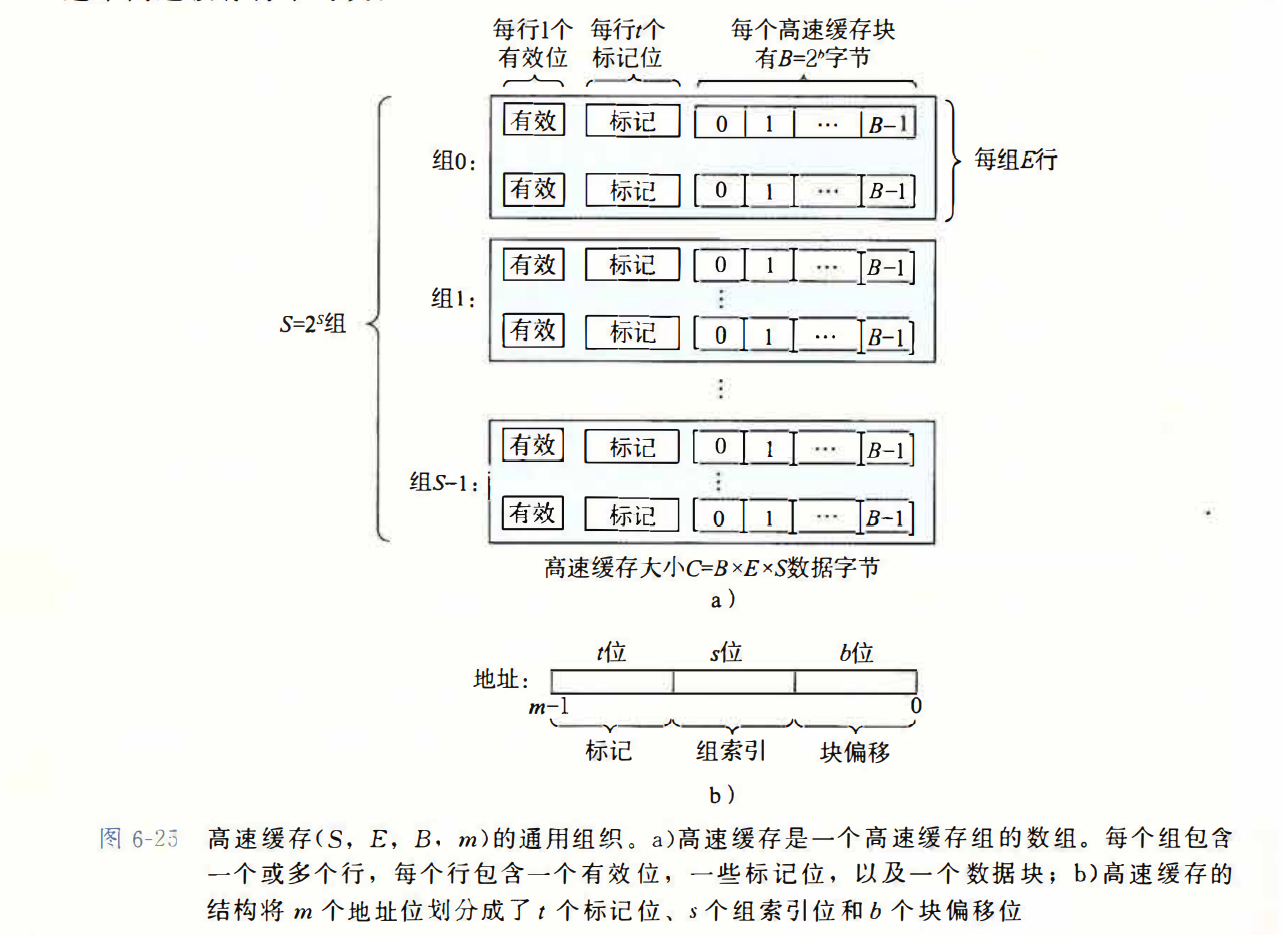

通用的高速缓存存储器组织结构

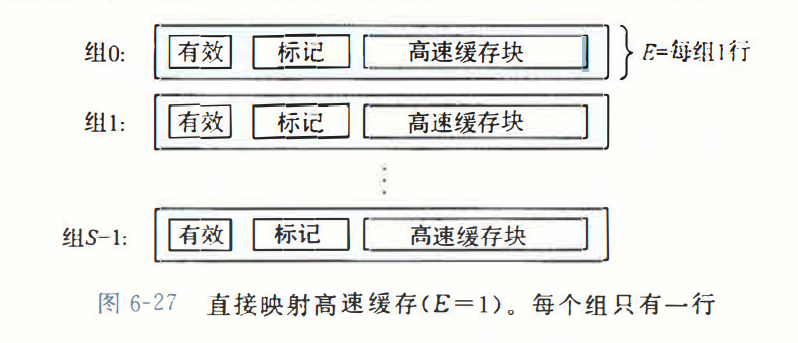

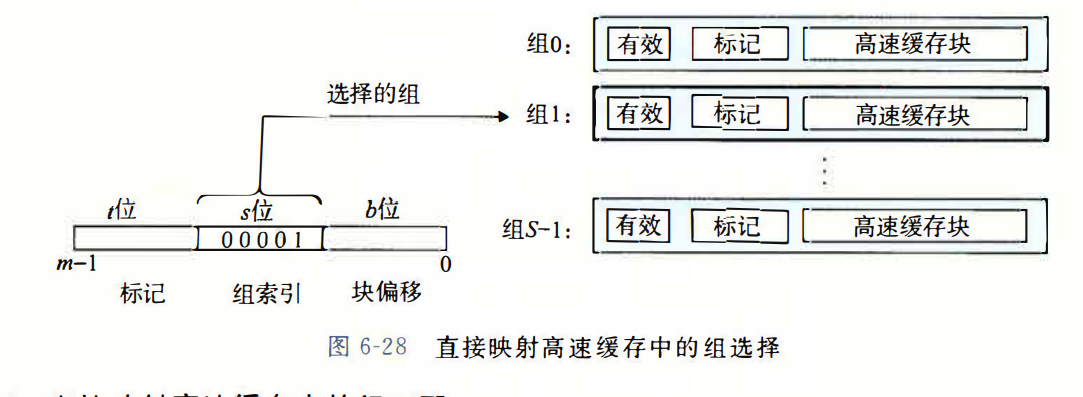

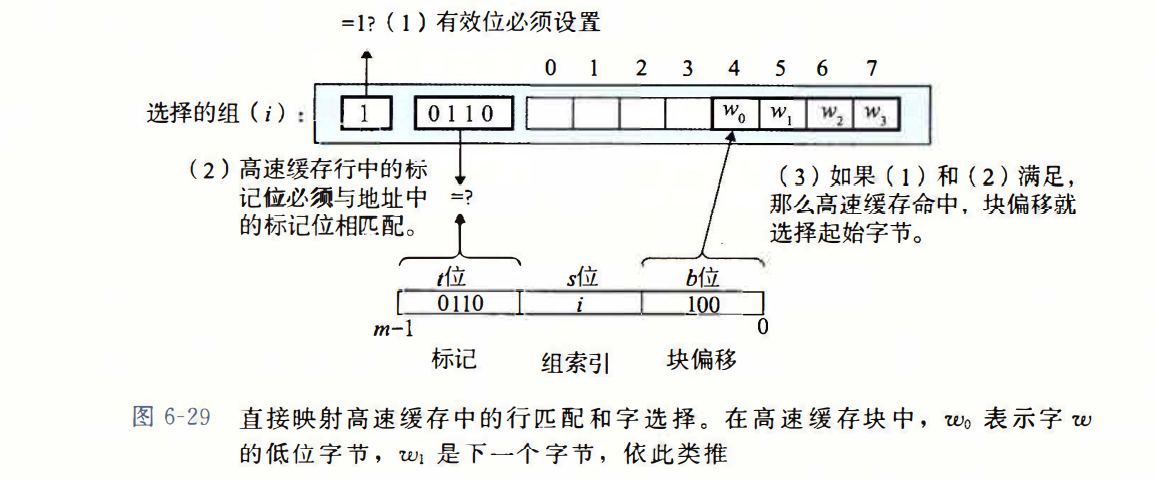

直接映射高速缓存

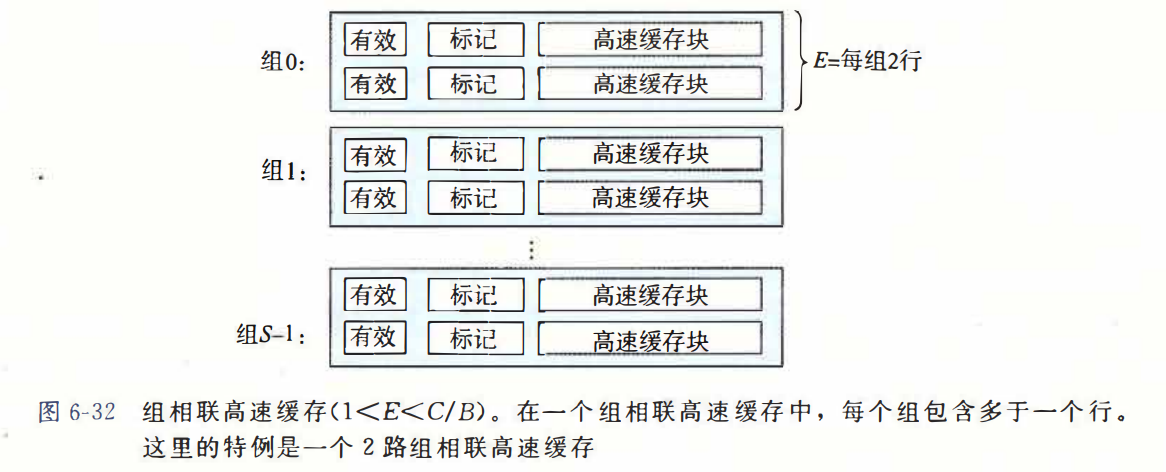

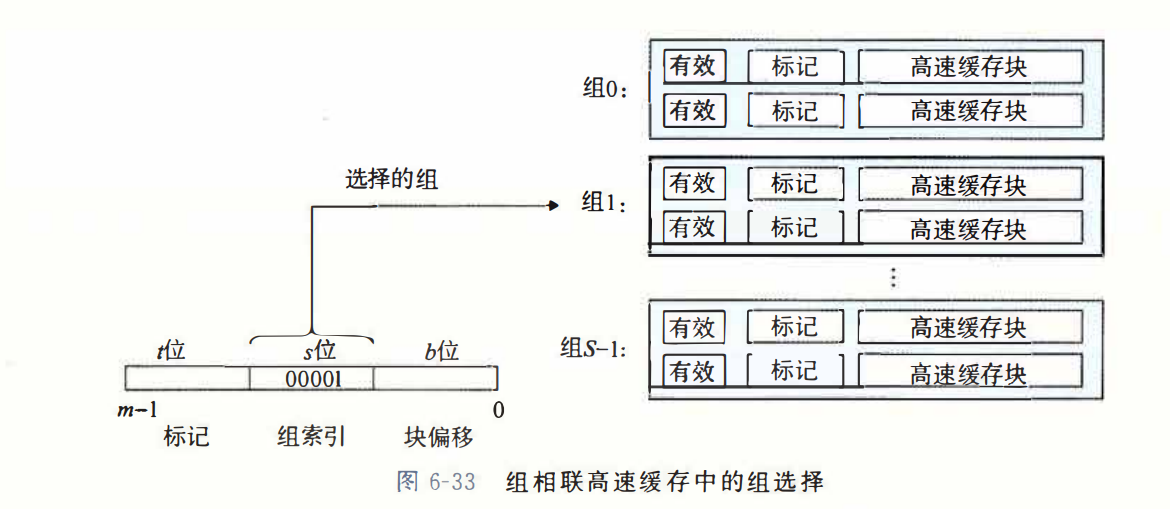

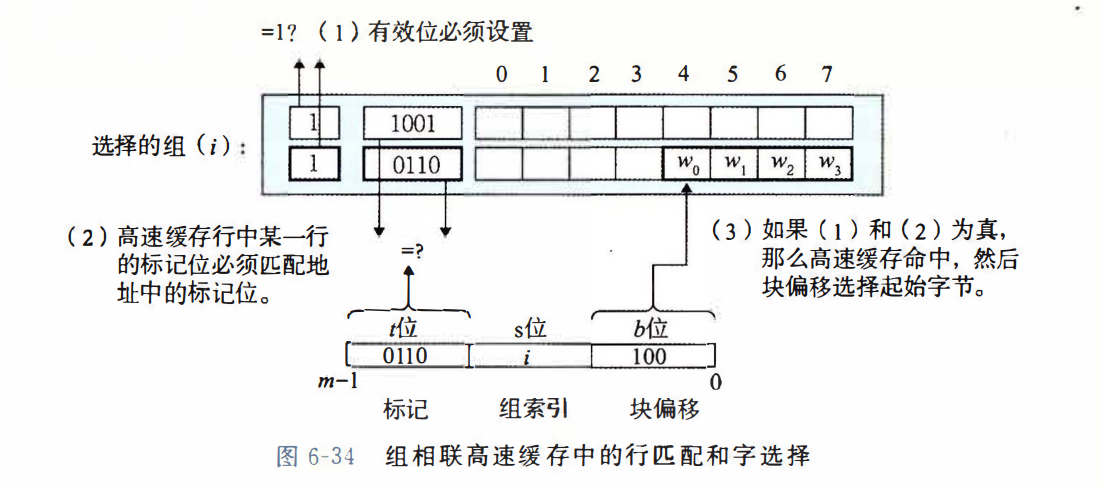

组相联高速缓存

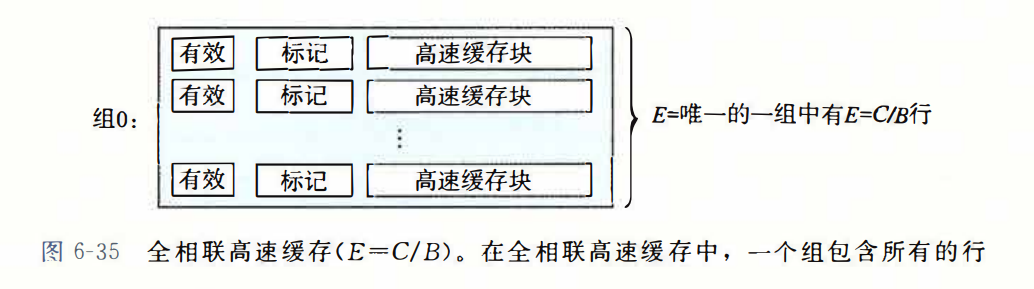

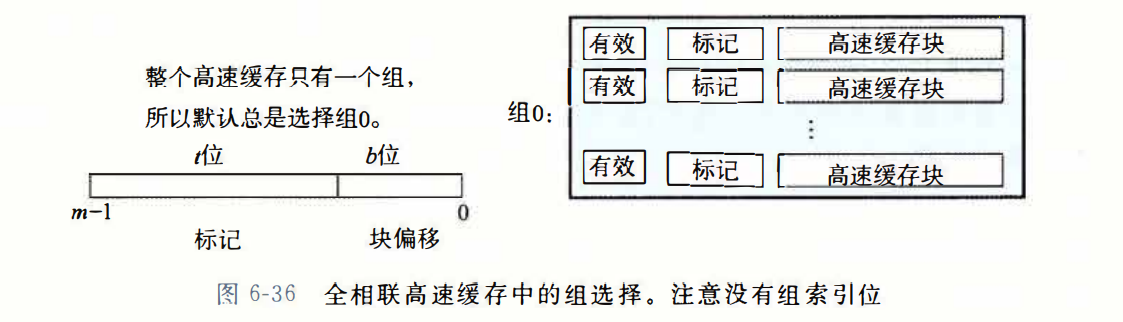

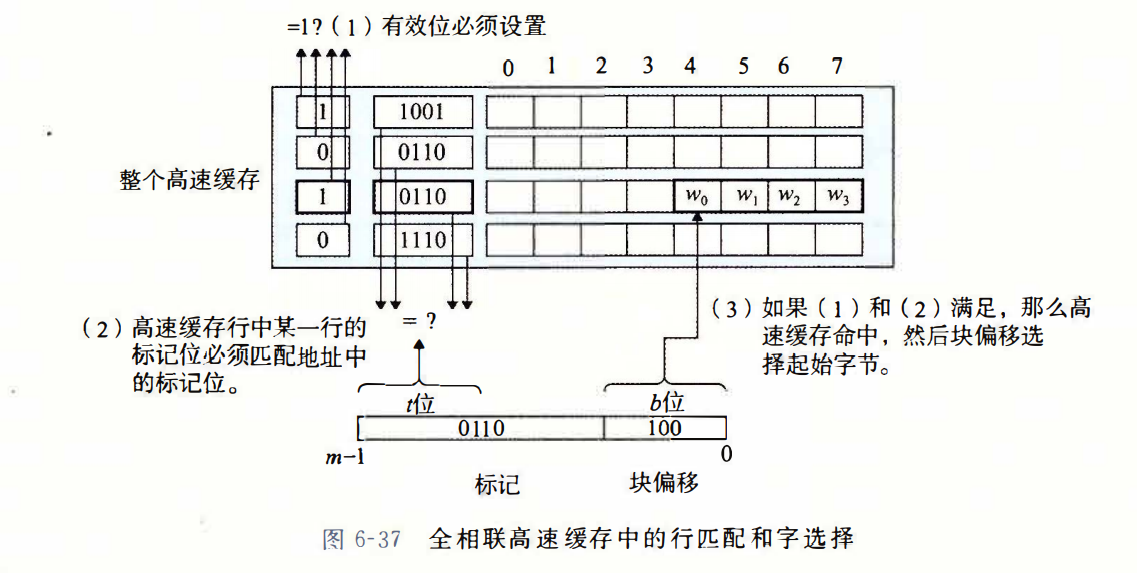

全相联高速缓存

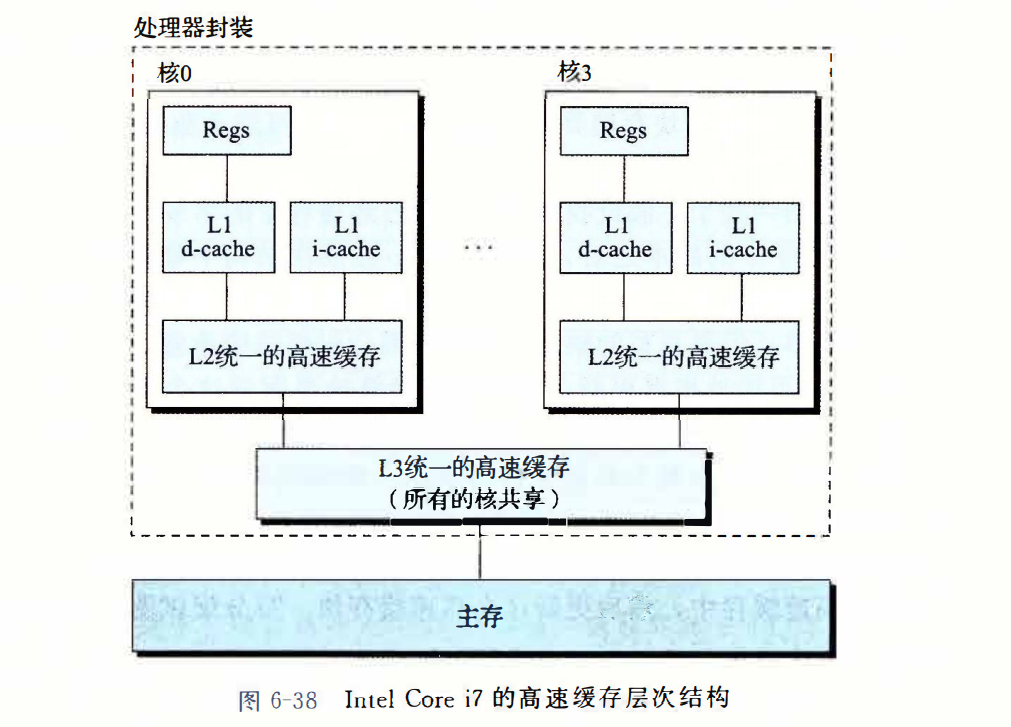

Intel Corei7高速缓存

编写高速缓存友好的代码

基本方法:

- 让最常见的情况运行得快;

- 尽量减小每个循环内部的缓存不命中数量。

存储器山